当前位置:

X-MOL 学术

›

Adv. Electron. Mater.

›

论文详情

Our official English website, www.x-mol.net, welcomes your

feedback! (Note: you will need to create a separate account there.)

3D Nano Hafnium-Based Ferroelectric Memory Vertical Array for High-Density and High-Reliability Logic-In-Memory Application

Advanced Electronic Materials ( IF 5.3 ) Pub Date : 2024-11-19 , DOI: 10.1002/aelm.202400438 Jiajie Yu, Tianyu Wang, Chen Lu, Zhenhai Li, Kangli Xu, Yongkai Liu, Yifan Song, Jialin Meng, Hao Zhu, Qingqing Sun, David Wei Zhang, Lin Chen

Advanced Electronic Materials ( IF 5.3 ) Pub Date : 2024-11-19 , DOI: 10.1002/aelm.202400438 Jiajie Yu, Tianyu Wang, Chen Lu, Zhenhai Li, Kangli Xu, Yongkai Liu, Yifan Song, Jialin Meng, Hao Zhu, Qingqing Sun, David Wei Zhang, Lin Chen

|

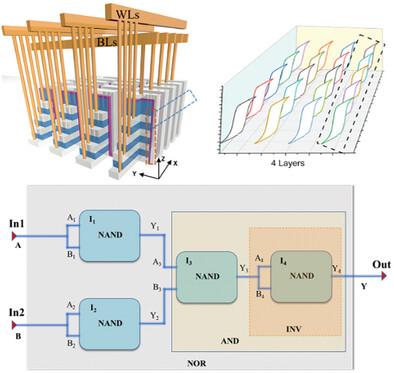

A new type of ferroelectric memory device with high reliability and complementary metal-oxide-semiconductor (CMOS) compatibility characteristics is an important condition for achieving integrated memory and computing chips. Here, 3D stacked ferroelectric memory devices based on ferroelectric materials of HfO2 are fabricated. The device exhibits high speed (50 ns), low read voltage (0.5 V), and great reliability with no substantial degradation after 1010 cycles and a 10-years data retention at 85 °C. The IMP and NAND logic are achieved with stable memory window (>200 mV) across the vertical devices’ interconnection. On this basis, combining with the traditional CMOS logic device, multiple combination logic functions containing NOT, AND, and NOR are achieved by simulation. The collaboration of devices in the vertical direction providing the possibility of combining multi-bit logic in memory functions and paves the way for the implementation of high-density, high-reliability, and low-energy consumption computing-in-memory chips compatible with the CMOS technology.

中文翻译:

用于高密度和高可靠性逻辑内存应用的 3D 纳米铪基铁电存储器垂直阵列

一种具有高可靠性和互补金属氧化物半导体 (CMOS) 兼容性的新型铁电存储器件是实现集成存储和计算芯片的重要条件。在这里,基于 HfO2 的铁电材料制造了 3D 堆叠铁电存储器件。该器件具有高速 (50 ns)、低读取电压 (0.5 V) 和高可靠性,在 10 到10 次循环后没有实质性退化,并且在 85 °C 下可保持 10 年的数据。 IMP 和 NAND 逻辑是通过垂直设备互连的稳定内存窗口 (>200 mV) 实现的。在此基础上,结合传统的 CMOS 逻辑器件,通过仿真实现包含 NOT、AND、NOR 的多种组合逻辑功能。器件在垂直方向上的协作提供了在内存功能中结合多位逻辑的可能性,并为实现与 CMOS 技术兼容的高密度、高可靠性和低能耗的内存计算芯片铺平了道路。

更新日期:2024-11-20

中文翻译:

用于高密度和高可靠性逻辑内存应用的 3D 纳米铪基铁电存储器垂直阵列

一种具有高可靠性和互补金属氧化物半导体 (CMOS) 兼容性的新型铁电存储器件是实现集成存储和计算芯片的重要条件。在这里,基于 HfO2 的铁电材料制造了 3D 堆叠铁电存储器件。该器件具有高速 (50 ns)、低读取电压 (0.5 V) 和高可靠性,在 10 到10 次循环后没有实质性退化,并且在 85 °C 下可保持 10 年的数据。 IMP 和 NAND 逻辑是通过垂直设备互连的稳定内存窗口 (>200 mV) 实现的。在此基础上,结合传统的 CMOS 逻辑器件,通过仿真实现包含 NOT、AND、NOR 的多种组合逻辑功能。器件在垂直方向上的协作提供了在内存功能中结合多位逻辑的可能性,并为实现与 CMOS 技术兼容的高密度、高可靠性和低能耗的内存计算芯片铺平了道路。

京公网安备 11010802027423号

京公网安备 11010802027423号