当前位置:

X-MOL 学术

›

Small Methods

›

论文详情

Our official English website, www.x-mol.net, welcomes your

feedback! (Note: you will need to create a separate account there.)

Approaching Ohmic Contacts for Ideal Monolayer MoS2 Transistors Through Sulfur-Vacancy Engineering

Small Methods ( IF 10.7 ) Pub Date : 2023-08-07 , DOI: 10.1002/smtd.202300611 Jiankun Xiao 1 , Kuanglei Chen 1 , Xiankun Zhang 1, 2 , Xiaozhi Liu 3 , Huihui Yu 1 , Li Gao 1 , Mengyu Hong 1 , Lin Gu 3 , Zheng Zhang 1, 2 , Yue Zhang 1, 2

Small Methods ( IF 10.7 ) Pub Date : 2023-08-07 , DOI: 10.1002/smtd.202300611 Jiankun Xiao 1 , Kuanglei Chen 1 , Xiankun Zhang 1, 2 , Xiaozhi Liu 3 , Huihui Yu 1 , Li Gao 1 , Mengyu Hong 1 , Lin Gu 3 , Zheng Zhang 1, 2 , Yue Zhang 1, 2

Affiliation

|

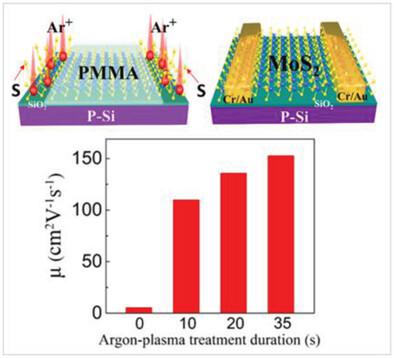

Field-effect transistors (FETs) made of monolayer 2D semiconductors (e.g., MoS2) are among the basis of the future modern wafer chip industry. However, unusually high contact resistances at the metal-semiconductor interfaces have seriously limited the improvement of monolayer 2D semiconductor FETs so far. Here, a high-scale processable strategy is reported to achieve ohmic contact between the metal and monolayer MoS2 with a large number of sulfur vacancies (SVs) by using simple sulfur-vacancy engineering. Due to the successful doping of the contact regions by introducing SVs, the contact resistance of monolayer MoS2 FET is as low as 1.7 kΩ·µm. This low contact resistance enables high-performance MoS2 FETs with ultrahigh carrier mobility of 153 cm2 V−1 s−1, a large on/off ratio of 4 × 109, and high saturation current of 342 µA µm−1. With the comprehensive investigation of different SV concentrations by adjusting the plasma duration, it is also demonstrated that the SV-increased electron doping, with its resulting reduced Schottky barrier, is the dominant factor driving enhanced electrical performance. The work provides a simple method to promote the development of industrialized atomically thin integrated circuits.

中文翻译:

通过硫空位工程接近理想单层 MoS2 晶体管的欧姆接触

由单层二维半导体(例如MoS 2 )制成的场效应晶体管(FET)是未来现代晶圆芯片行业的基础。然而,迄今为止,金属-半导体界面异常高的接触电阻严重限制了单层二维半导体FET的改进。在此,报道了一种大规模可加工策略,通过使用简单的硫空位工程实现金属和具有大量硫空位(SV)的单层MoS 2之间的欧姆接触。由于通过引入SV成功地对接触区进行掺杂,单层MoS 2 FET的接触电阻低至1.7 kΩ·μm。这种低接触电阻使得高性能MoS 2 FET具有153 cm 2 V -1 s -1的超高载流子迁移率、4 × 10 9的大开/关比以及342 µA µm -1的高饱和电流。通过调整等离子体持续时间对不同 SV 浓度进行综合研究,还证明了 SV 增加的电子掺杂及其导致的肖特基势垒降低,是推动电气性能增强的主导因素。该工作为促进工业化原子薄集成电路的发展提供了一种简单的方法。

更新日期:2023-08-07

中文翻译:

通过硫空位工程接近理想单层 MoS2 晶体管的欧姆接触

由单层二维半导体(例如MoS 2 )制成的场效应晶体管(FET)是未来现代晶圆芯片行业的基础。然而,迄今为止,金属-半导体界面异常高的接触电阻严重限制了单层二维半导体FET的改进。在此,报道了一种大规模可加工策略,通过使用简单的硫空位工程实现金属和具有大量硫空位(SV)的单层MoS 2之间的欧姆接触。由于通过引入SV成功地对接触区进行掺杂,单层MoS 2 FET的接触电阻低至1.7 kΩ·μm。这种低接触电阻使得高性能MoS 2 FET具有153 cm 2 V -1 s -1的超高载流子迁移率、4 × 10 9的大开/关比以及342 µA µm -1的高饱和电流。通过调整等离子体持续时间对不同 SV 浓度进行综合研究,还证明了 SV 增加的电子掺杂及其导致的肖特基势垒降低,是推动电气性能增强的主导因素。该工作为促进工业化原子薄集成电路的发展提供了一种简单的方法。

京公网安备 11010802027423号

京公网安备 11010802027423号