当前位置:

X-MOL 学术

›

Mater. Horiz.

›

论文详情

Our official English website, www.x-mol.net, welcomes your

feedback! (Note: you will need to create a separate account there.)

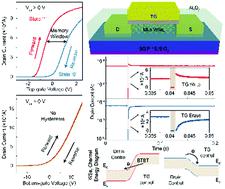

The floating body effect of a WSe2 transistor with volatile memory performance

Materials Horizons ( IF 12.2 ) Pub Date : 2022-06-10 , DOI: 10.1039/d2mh00151a Zhan-Peng Wang , Peng Xie , Jing-Yu Mao , Ruopeng Wang , Jia-Qin Yang , Zihao Feng , Ye Zhou , Chi-Ching Kuo , Su-Ting Han

Materials Horizons ( IF 12.2 ) Pub Date : 2022-06-10 , DOI: 10.1039/d2mh00151a Zhan-Peng Wang , Peng Xie , Jing-Yu Mao , Ruopeng Wang , Jia-Qin Yang , Zihao Feng , Ye Zhou , Chi-Ching Kuo , Su-Ting Han

|

The floating body effect in Meta-Stable-Dip RAM (MSDRAM) has been broadly employed in implementing single-transistor capacitor-less (1T0C) dynamic random access memory (DRAM) cells to break through the limitation of finite size reduction of peripheral capacitors. However, the majority of them were broadly demonstrated in conventional CMOS technology, while emerging semiconductor systems are rarely explored. Here, we creatively explore exfoliated multilayer tungsten diselenide (WSe2) for the application of 1T0C DRAM, breaking the limitation of channel thickness in the traditional architecture. Through the comparison of the electrical characteristics among three dual-gate transistors with different lengths of top-gate, we demonstrated the essential role of the floating body effect in achieving the function of 1T0C DRAM displaying two distinct states that are differentiated by hole population within the floating body. Moreover, according to the analysis of in situ electrostatic force microscopy (EFM) measurements and theoretical calculation via density functional theory (DFT), the injection of holes through band-to-band (B2B) tunneling can be ascribed to the effectively electrostatic modulation. These consequences prove our innovative concept to achieve the function of 1T0C DRAM through employing the ML WSe2, which is a vital step toward the breakthrough of the inherent limitations of DRAM cells.

中文翻译:

具有易失性存储器性能的 WSe2 晶体管的浮体效应

Meta-Stable-Dip RAM (MSDRAM) 中的浮体效应已广泛应用于实现单晶体管无电容器 (1T0C) 动态随机存取存储器 (DRAM) 单元,以突破外围电容器有限尺寸减小的限制。然而,它们中的大多数在传统的 CMOS 技术中得到了广泛的展示,而新兴的半导体系统却很少被探索。在这里,我们创造性地探索了剥落的多层二硒化钨(WSe 2)针对1T0C DRAM的应用,打破了传统架构中通道厚度的限制。通过比较具有不同顶栅长度的三个双栅晶体管之间的电气特性,我们证明了浮体效应在实现 1T0C DRAM 的功能中的重要作用,该 DRAM 显示出两种不同的状态,这两种状态由内部的空穴数量来区分。浮体。此外,根据原位静电力显微镜 (EFM) 测量分析和理论计算在密度泛函理论 (DFT) 中,通过带间 (B2B) 隧穿注入空穴可归因于有效的静电调制。这些结果证明了我们通过采用ML WSe 2实现1T0C DRAM功能的创新理念,这是突破DRAM单元固有限制的重要一步。

更新日期:2022-06-10

中文翻译:

具有易失性存储器性能的 WSe2 晶体管的浮体效应

Meta-Stable-Dip RAM (MSDRAM) 中的浮体效应已广泛应用于实现单晶体管无电容器 (1T0C) 动态随机存取存储器 (DRAM) 单元,以突破外围电容器有限尺寸减小的限制。然而,它们中的大多数在传统的 CMOS 技术中得到了广泛的展示,而新兴的半导体系统却很少被探索。在这里,我们创造性地探索了剥落的多层二硒化钨(WSe 2)针对1T0C DRAM的应用,打破了传统架构中通道厚度的限制。通过比较具有不同顶栅长度的三个双栅晶体管之间的电气特性,我们证明了浮体效应在实现 1T0C DRAM 的功能中的重要作用,该 DRAM 显示出两种不同的状态,这两种状态由内部的空穴数量来区分。浮体。此外,根据原位静电力显微镜 (EFM) 测量分析和理论计算在密度泛函理论 (DFT) 中,通过带间 (B2B) 隧穿注入空穴可归因于有效的静电调制。这些结果证明了我们通过采用ML WSe 2实现1T0C DRAM功能的创新理念,这是突破DRAM单元固有限制的重要一步。

京公网安备 11010802027423号

京公网安备 11010802027423号