当前位置:

X-MOL 学术

›

Int. J. Circ. Theory Appl.

›

论文详情

Our official English website, www.x-mol.net, welcomes your

feedback! (Note: you will need to create a separate account there.)

半选无干扰 8T 低泄漏 SRAM 单元

International Journal of Circuit Theory and Applications ( IF 1.8 ) Pub Date : 2022-02-02 , DOI: 10.1002/cta.3232 Rohit Lorenzo 1 , Roy Paily 2

International Journal of Circuit Theory and Applications ( IF 1.8 ) Pub Date : 2022-02-02 , DOI: 10.1002/cta.3232 Rohit Lorenzo 1 , Roy Paily 2

Affiliation

|

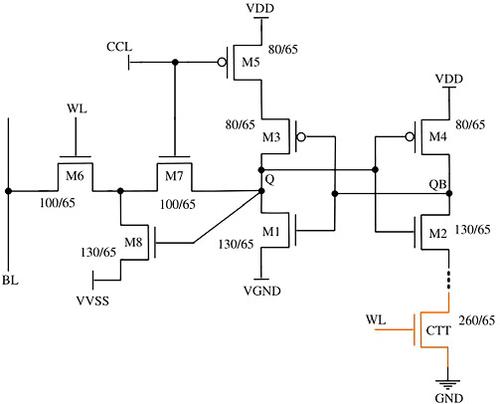

这项工作提出了一种稳健且低泄漏的新型 8T 静态随机存取存储器 (SRAM) 单元,没有任何半选择干扰。所提议的单元通过消除来自电源和接地的轨迹来消除写入干扰。此外,它通过将读取路径与存储节点分离来消除读取干扰。所提出的单元通过使用不同的控制信号来解决半选的挑战。由于虚拟接地 (VGND)、串联尾晶体管和接入串联堆叠晶体管,该单元实现了低泄漏。为了研究所提出的 SRAM 的实用性,将其与 6T、10T、9T、PG9T、7T 和 8T SRAM 单元进行了比较。所提出的 SRAM 将泄漏功率、写入功率和读取功率降低了 12.4%、21.62% 和 29.06%。此外,所提出的单元将读写噪声容限提高了 57.19% 和 19.96%,分别与传统的 6T SRAM 相比。同样,与 10T SRAM 相比,写入能耗降低至约 43.86 倍,而读取能耗降低至 28.95 倍。

"点击查看英文标题和摘要"

更新日期:2022-02-02

"点击查看英文标题和摘要"

京公网安备 11010802027423号

京公网安备 11010802027423号