当前位置:

X-MOL 学术

›

Int. J. Circ. Theory Appl.

›

论文详情

Our official English website, www.x-mol.net, welcomes your

feedback! (Note: you will need to create a separate account there.)

Design of low power approximate floating‐point adders

International Journal of Circuit Theory and Applications ( IF 1.8 ) Pub Date : 2020-06-27 , DOI: 10.1002/cta.2831 Reza Omidi 1 , Sepehr Sharifzadeh 2

International Journal of Circuit Theory and Applications ( IF 1.8 ) Pub Date : 2020-06-27 , DOI: 10.1002/cta.2831 Reza Omidi 1 , Sepehr Sharifzadeh 2

Affiliation

|

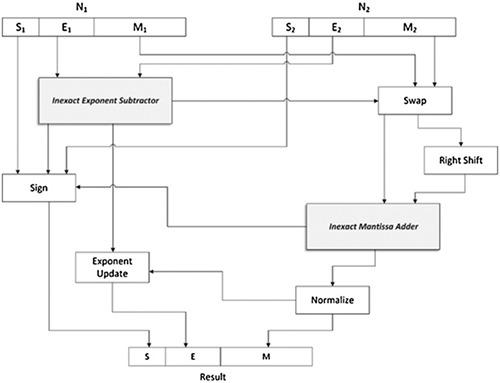

Due to the increasing demands for more power in data intensive computing, low power design methodologies play a very important role in these systems. For noncritical data, the approximate computing that significantly reduces the power can be used. In this paper, an approximate floating‐point adder is proposed by designing an inexact mantissa adder and exponent subtractor. The results indicate that the power consumption and delay of the proposed approximate floating‐point adder have been decreased by 37% and 62% compared with the IEEE‐754 single‐precision floating‐point (FP) adder. Furthermore, compared with a state‐of‐the‐art inexact floating‐point adder, the proposed method provides an improvement of 7% and 21% in terms of the power consumption and delay. In addition, the proposed floating‐point adder has been investigated in terms of error, and the mean error of the proposed floating‐point adder at worst is about 55% less than that of another approximate floating‐point adder considered in this work. High dynamic range (HDR) images are processed using the proposed approximate floating‐point adders to show the performance of the proposed adder. The results show that, on average, peak signal‐to‐noise ratio increased by 9.6 and 18.64 dB, which may be achieved by utilizing the proposed floating‐point adder.

中文翻译:

低功耗近似浮点加法器的设计

由于数据密集型计算中对更多功能的需求不断增长,因此低功耗设计方法在这些系统中起着非常重要的作用。对于非关键数据,可以使用可显着降低功耗的近似计算。本文通过设计不精确的尾数加法器和指数减法器,提出了一种近似浮点加法器。结果表明,与IEEE-754单精度浮点(FP)加法器相比,拟议的近似浮点加法器的功耗和延迟分别降低了37%和62%。此外,与最先进的不精确浮点加法器相比,该方法在功耗和延迟方面分别提高了7%和21%。此外,还针对误差对所提出的浮点加法器进行了研究,拟议的浮点加法器在最坏的情况下的平均误差比本工作中考虑的另一个近似浮点加法器的平均误差小约55%。使用建议的近似浮点加法器处理高动态范围(HDR)图像,以显示建议的加法器的性能。结果表明,平均而言,峰值信噪比提高了9.6和18.64 dB,这可以通过使用建议的浮点加法器来实现。

更新日期:2020-06-27

中文翻译:

低功耗近似浮点加法器的设计

由于数据密集型计算中对更多功能的需求不断增长,因此低功耗设计方法在这些系统中起着非常重要的作用。对于非关键数据,可以使用可显着降低功耗的近似计算。本文通过设计不精确的尾数加法器和指数减法器,提出了一种近似浮点加法器。结果表明,与IEEE-754单精度浮点(FP)加法器相比,拟议的近似浮点加法器的功耗和延迟分别降低了37%和62%。此外,与最先进的不精确浮点加法器相比,该方法在功耗和延迟方面分别提高了7%和21%。此外,还针对误差对所提出的浮点加法器进行了研究,拟议的浮点加法器在最坏的情况下的平均误差比本工作中考虑的另一个近似浮点加法器的平均误差小约55%。使用建议的近似浮点加法器处理高动态范围(HDR)图像,以显示建议的加法器的性能。结果表明,平均而言,峰值信噪比提高了9.6和18.64 dB,这可以通过使用建议的浮点加法器来实现。

京公网安备 11010802027423号

京公网安备 11010802027423号