中国科学院微电子研究所与北京华碳元芯电子科技公司联合研发基于碳基CMOSPDK超大规模集成电路设计流程并通过SRAM芯片流片验证

本篇文章版权为 尹明会所有,未经授权禁止转载。

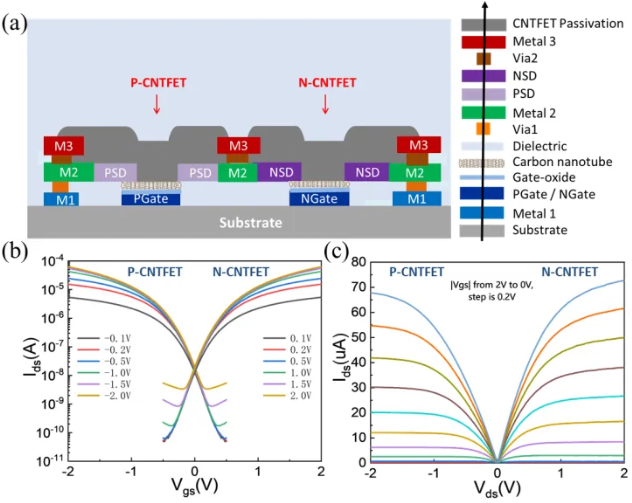

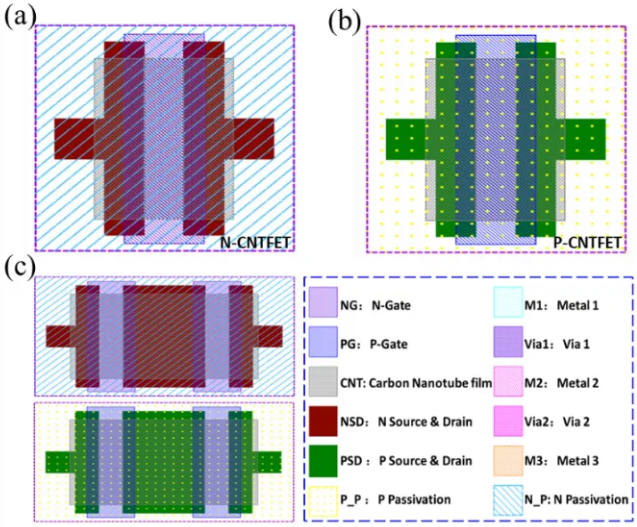

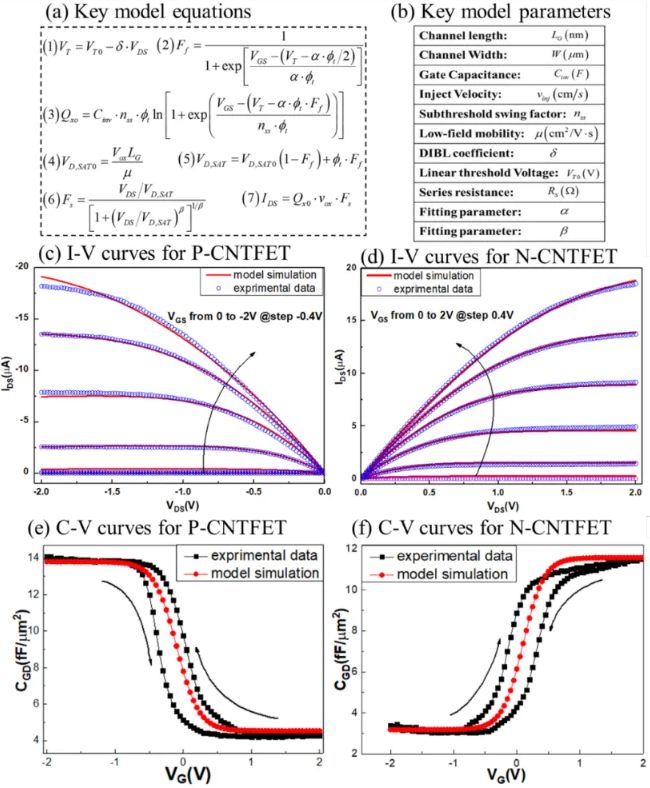

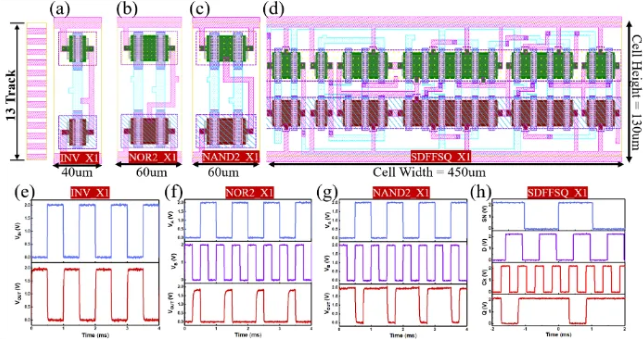

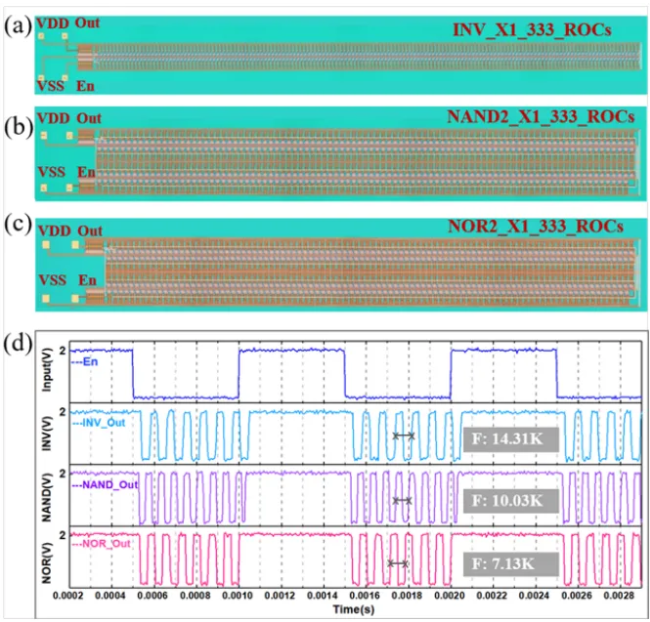

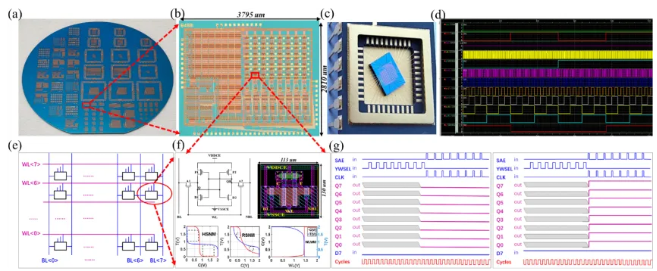

背景介绍 碳纳米管场效应晶体管(CNTFETs)具有优异的电学特性,如弹道输运、高饱和速度和本征电容小等,被认为是设计高性能、低功耗和高密度集成电路的有力候选者。综合来看,硅基集成电路设计已有近半个世纪的技术积累,碳基集成电路设计流程需要和硅基设计流程部分兼容甚至完全兼容:一方面可以极大地节约电子设计自动化EDA工具研发等“硬”成本,另一方面也可以借鉴甚至直接使用成熟的硅基EDA工具平台,从而节省碳基芯片研发所需的时间和经济等“软”成本。这就需要研发与硅基EDA工具兼容的碳基工艺PDK数据包,解决碳基集成电路设计的差异性和设计效率问题。中国科学院微电子研究所与北京华碳元芯电子科技有限责任公司合作,研发了兼容碳基工艺的PDK,在传统EDA工具中实现了基于碳基PDK的大规模集成电路设计流程,完成了64bitSRAM单元的设计并流片成功。本工作有效提升了碳基集成电路设计效率,对碳基芯片技术工程化和产业化进程起到推动作用。 成果简介 本研究基于北京华碳元芯电子科技有限责任公司的3μm碳基CMOS工艺,由中国科学院微电子研究所物理IP课题组开发了一套与硅基VLSI设计流程兼容的晶圆级3µm碳基CMOS工艺PDK,其中碳纳米管场效应管器件的接触孔栅间距(CGP)是21μm,标准单元的门密度为128门/mm²和554个晶体管/mm²。项目双方通力合作,成功完成了碳基逻辑门、SRAM Cell、333阶的环形振荡器等的逻辑器件的设计和流片,证明PDK的正确性和有效性。测试结果显示,反相器、与门、或门和触发器的门延迟分别为105 ns,150 ns,210 ns和406 ns。在上述工作的基础上,项目组最终设计实现了带有完整外围读写驱动电路的SRAM64bit电路系统,其时序、功耗、面积分别为10 kHz, 112.1µW, 3795µm×2810 µm。该研究证实了碳基集成电路设计可以与现有的硅基EDA工具及集成电路设计流程兼容。典型数模混合电路SRAM128×8的实现,代表碳基集成电路又向前迈出了重要而有意义的一步。 图文导读 图1 底栅工艺CNTFETs器件结构示意图与器件特性曲线。(a)P型与N型CNFET器件结构示意图;(b)P型与N型CNFET传输特性测试曲线,具备较大的开关比;(c)P型与N型CNFET输出具备良好的对称性。 图2 P型与N型CNFET器件版图。(a)N性CNTFET器件;(b)P型CNTFET器件;(c)N型与P型CNFET共源结构。 图3 碳基MOSFET紧凑模型概览。(a)模型核心方程;(b)模型关键参数;(c)(d)模型测试数据与仿真结果比较;(e)(f)基于预测与经验参数的CV特性曲线。 图4 碳基INV, NOR, NAND和SDFFSQ标准单元版图与测试波形。 图5 多阶环形振荡电路测试验证。 图6 晶圆级集成电路设计与展示。(a)64bitCNFETSRAM晶圆展示;(b)64bitCNFETSRAM器件光罩;(c)64bit CNFET SRAM封装后的芯片;(d)64bit CNFET SRAM仿真结果;(e)64bit CNFET SRAM电路图;(f)6TSRAM单元的电路图、版图、保持裕度、读裕度、写裕度;(g)64bit CNFET SRAM全0全1测试结果。 作者简介 文章信息 Yin M, Xu H, You Y, et al. Wafer-scale carbon-based CMOS PDK compatible with silicon-based VLSI design flow. Nano Research, 2024, https://doi.org/10.1007/s12274-024-6583-8.

如果篇首注明了授权来源,任何转载需获得来源方的许可!如果篇首未特别注明出处,本文版权属于 X-MOL ( x-mol.com ), 未经许可,谢绝转载!

京公网安备 11010802027423号

京公网安备 11010802027423号