Nature子刊:“娇贵”电子材料,性质“即插即测”

随着硅基器件越来越接近摩尔定律的极限,研究者们也加快了对新一代电子材料的探索步伐,如二维半导体、卤化物钙钛矿等都展示了诱人的应用前景。要测试这些新兴电子材料的性质,需要将它们与器件的其他关键结构(如电极、介电层)紧密集成,这个过程却一直是个重要的挑战。传统的电子制造工艺,包括光刻、真空沉积和等离子体蚀刻等,是硅基器件的基础,但通常包含腐蚀性过程以及高能量过程,很容易导致这些“娇贵”的新兴电子材料出现结构缺陷,钙钛矿与活性化学物质接触时甚至会迅速降解,这将严重降低器件性能。如此一来,快速、准确地测试这些新兴电子材料的性质就无从谈起了。

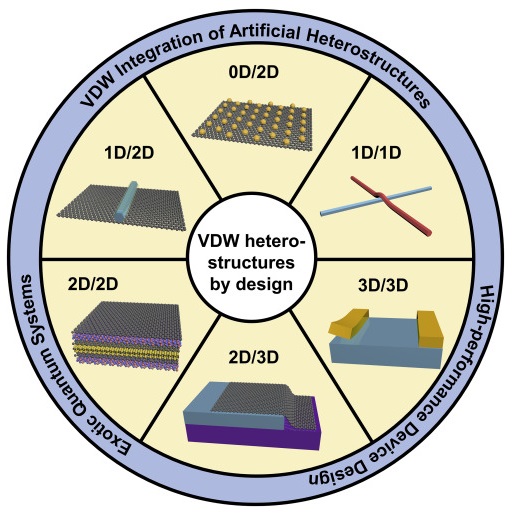

从零维到三维的异质结集成设计。图片来源:Matter [1]

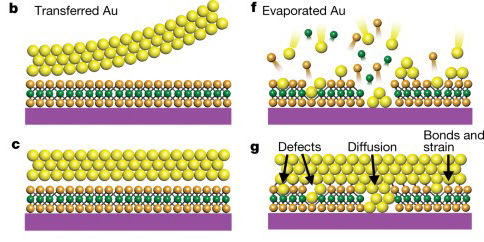

范德华(vdW)异质结构,为新型材料提供了一种低能量的加工方法,没有直接化学键合的弱相互作用,保证了各组分的原子结构和固有的电子特性,不同材料在界面处不会产生严重的应变或晶格无序,也为不同维度的异质结构设计提供了机遇和可能。早在2018年,美国加利福尼亚大学洛杉矶分校段镶锋教授(点击查看介绍)课题组就在Nature 杂志上发表论文 [2],论证了传统的金属蒸镀极易让半导体材料出现严重的缺陷,而转移电极可以得到原子级平整的界面。

转移和蒸镀的金属半导体异质结对比示意图。图片来源:Nature [2]

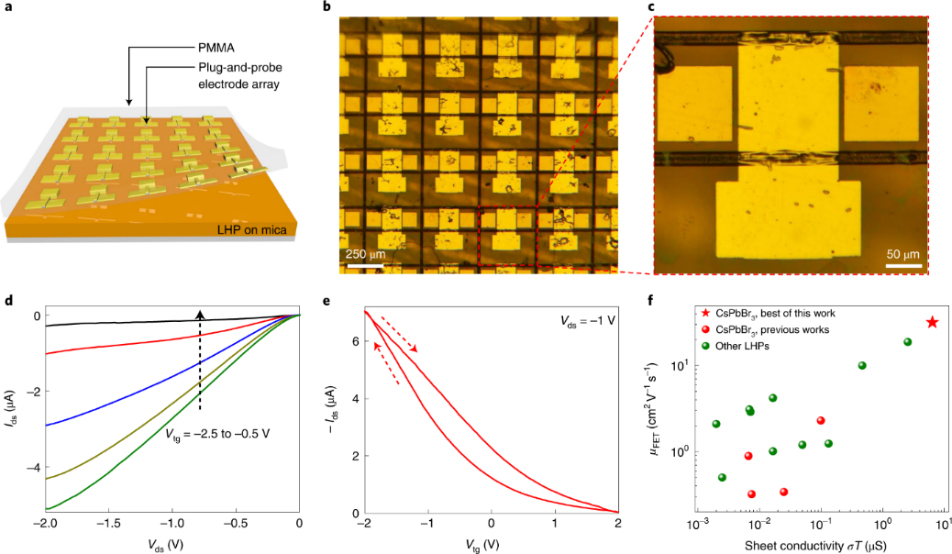

近日,段镶锋教授课题组又在Nature Nanotechnology 杂志上发表论文,开发了一种便捷通用的“即插即测(plug-and-probe)”方法,通过一步转移和层压工艺,在电子材料上实现接触层和高k介电层的“无损伤”同时vdW集成。这种方法避免了在活性材料界面上的直接光刻或沉积,将接触层和介电层的高能制造与器件集成分开,可以制造具有极高界面质量的顶栅晶体管。他们在MoS2表面搭建了“即插即测”顶栅晶体管,亚阈值摆幅为60 mV/dec。将该方法用于卤化铅钙钛矿,他们实现了一个高k顶栅CsPbBr3晶体管,具有低工作电压和非常高的双端场效应迁移率(32 cm2 V−1 s−1)。该方法可以拓展至厘米级MoS2和钙钛矿材料,并生成顶栅晶体管阵列,为新兴材料固有电学特性的研究提供了一种快速、方便的器件制备和测量方法。

高k氧化物介电层和衬底之间一般具有强粘附性,为了实现有效的转移和集成,研究者以单层石墨烯作为牺牲层。随后,在表面沉积Y2O3介电层和金属源/漏电极,再剥离并转移至目标半导体材料上,就可以获得完整的顶栅顶接触器件。表征结果显示,界面处原子排列整齐,无明显的无序现象。整个工艺除最后一步外,只需要在牺牲层上进行,大大降低光刻、高能沉积等步骤对半导体材料的损伤。

一步法同时转移电极和Y2O3,无损伤地搭建顶栅晶体管。图片来源:Nat. Nanotechnol.

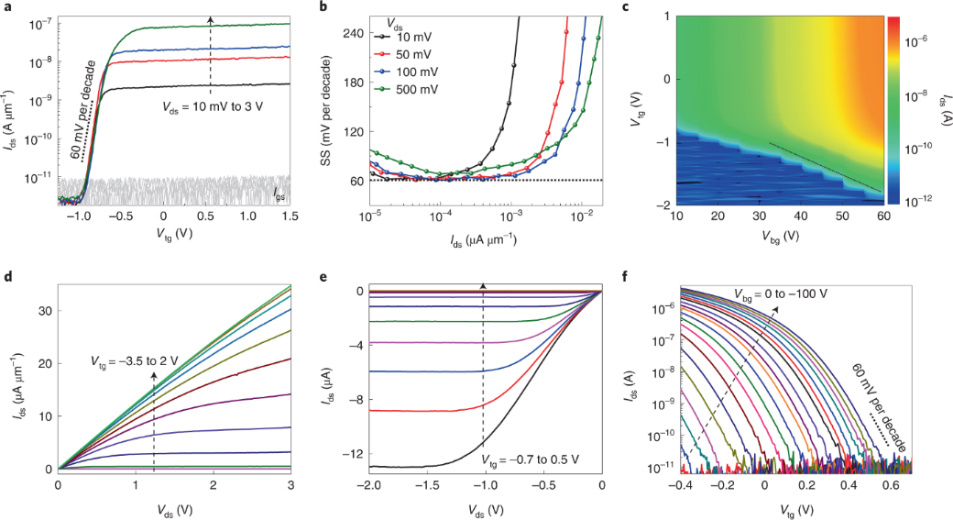

该方法制备的MoS2晶体管,转移特性曲线表现出优异的栅极可调性,亚阈值摆幅为60 mV/dec。电容-频率测试表明,总体陷阱密度约为1012 eV-1 cm-2,vdW接触界面平整清洁。类似地,在WSe2上转移介电层和电极,制备的p型顶栅晶体管亚阈值摆幅为75 mV/dec。

“即插即测”法制备二维材料晶体管性能。图片来源:Nat. Nanotechnol.

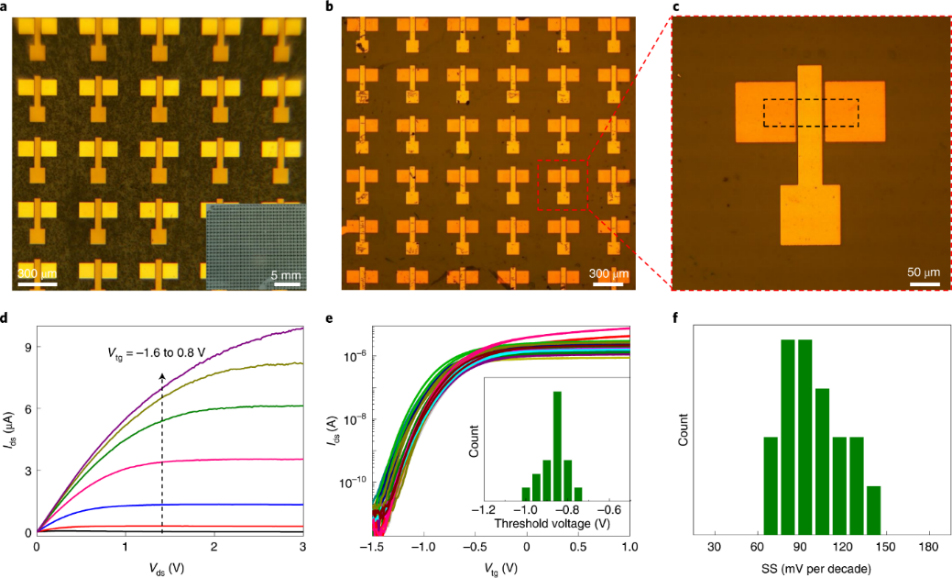

随后,研究者利用该方法在CVD生长的大面积MoS2表面制备了晶体管阵列,表现出高度的性能一致性。转移曲线显示出分布窄的特点,器件开关比均大于106,亚阈值摆幅分布在70-100 mV/dec之间。

“即插即测”法在大面积MoS2单层上制备晶体管阵列。图片来源:Nat. Nanotechnol.

卤化铅钙钛矿材料比较“娇贵”,与传统光刻工艺不兼容,使顶栅晶体管的制备极为困难。本文的“即插即测”法具有良好的可扩展性,为基于钙钛矿的晶体管阵列提供了理想的解决方案。器件的场效应迁移率可达32 cm2 V−1 s−1,vdW集成降低了器件的接触电阻。

“即插即测”法制备顶栅CsPbBr3晶体管阵列。图片来源:Nat. Nanotechnol.

“即插即测”法为顶栅晶体管的搭建提供了一种普适性的方法,器件材料间采用非键合的vdW集成,原始界面干净平整,这对于保持新型材料的固有电子特性至关重要。基于这种方法,可进一步开发可重复使用的“印章”探针,其器件架构嵌入在“印章”的底面上,这种“印章”探针可作为高效、无损伤工具用于快速测试新兴电子材料,而不需要器件制造步骤。此外,该方法制备的异质结界面间具有额外的扭转角自由度,这也可以为强相关系统中奇异量子特性的基础研究提供了一个广泛的平台。

原文(扫描或长按二维码,识别后直达原文页面,或点此查看原文):

A general one-step plug-and-probe approach to top-gated transistors for rapidly probing delicate electronic materials

Laiyuan Wang, Peiqi Wang, Jin Huang, Bosi Peng, Chuancheng Jia, Qi Qian, Jingyuan Zhou, Dong Xu, Yu Huang & Xiangfeng Duan

Nat. Nanotechnol., 2022, 17, 1206–1213, DOI: 10.1038/s41565-022-01221-1

导师介绍

段镶锋

https://www.x-mol.com/university/faculty/10154

参考文献:

[1] P. Wang, et al. Van der Waals Heterostructures by Design: From 1D and 2D to 3D. Matter, 2021, 4, 552-581. DOI: 10.1016/j.matt.2020.12.015

[2] Y. Liu, et al. Approaching the Schottky–Mott limit in van der Waals metal–semiconductor junctions. Nature 2018, 557, 696-700. DOI: 10.1038/s41586-018-0129-8

(本文由小希供稿)

如果篇首注明了授权来源,任何转载需获得来源方的许可!如果篇首未特别注明出处,本文版权属于 X-MOL ( x-mol.com ), 未经许可,谢绝转载!

-

Science:80后大牛造出“1纳米”晶体管 2016-10-23

-

高迁移率二维钙钛矿薄膜晶体管——有机共轭分子驱动的形貌调控 2021-10-05

-

直写高晶体管性能原子级厚二维半导体薄膜 2022-11-10

-

ACS Nano综述 | 面向下一代电子学应用的铁电二维器件 2022-09-22

-

Publisher Correction: Circumventing the stability problems of graphene nanoribbon zigzag edgesJames Lawrence, Alejandro Berdonces-Layunta, Shayan Edalatmanesh, Jesús Castro-Esteban, Tao Wang, Alejandro Jimenez-Martin, Bruno de la Torre, Rodrigo Castrillo-Bodero, Paula Angulo-Portugal, Mohammed S. G. Mohammed, Adam Matěj, Manuel Vilas-Varela, Frederik Schiller, Martina Corso, Pavel Jelinek, Diego Peña, Dimas G. de Oteyza

京公网安备 11010802027423号

京公网安备 11010802027423号