NE综述:二维材料在集成电路中的应用未来

先上一个听来的段子:

—“二维材料好像很热门,有什么实际应用呢?”

—“用途很多,目前主要用于制造博士……”

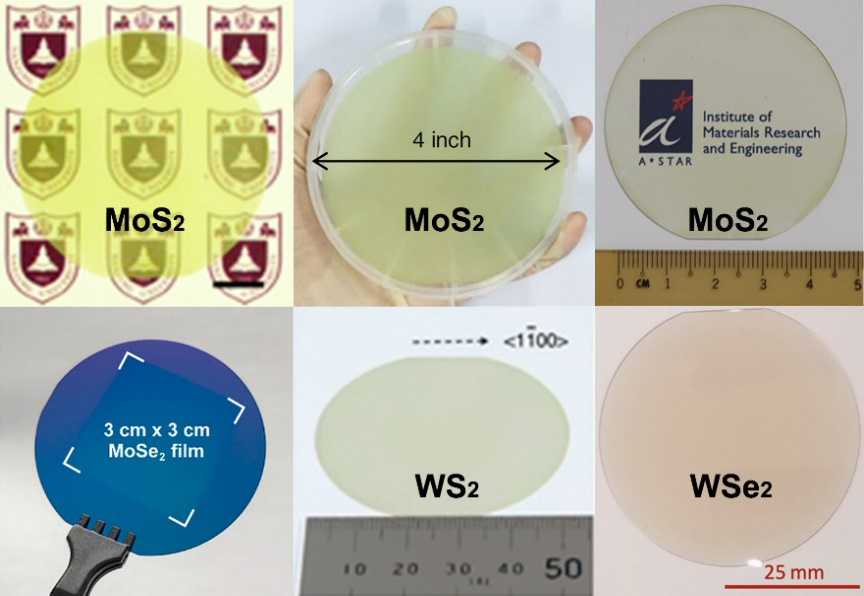

先不管段子好不好笑,二维材料大受追捧确是事实。尤其是在集成电路和电子器件领域,近几年来二维过渡金属硫化物(TMDs)、硒化物,如MoS2、WS2、MoSe2、WSe2等,纷纷实现了晶圆尺寸制备,被各大顶刊报道 [1-6],应用于晶体管及逻辑电路制备,并有望减轻短沟道效应,这使得二维材料走出实验室推进实际应用又向前了一步。

近日,美国宾夕法尼亚州立大学Saptarshi Das教授联合斯坦福大学、杜克大学等多家研究机构的学者,在Nature Electronics 杂志上发表综述,系统回顾了二维场效应晶体管的发展历史,讨论了关键性能指标,并展望了基于二维晶体管在超大规模集成电路(very large-scale integration, VLSI)中的优势与挑战。

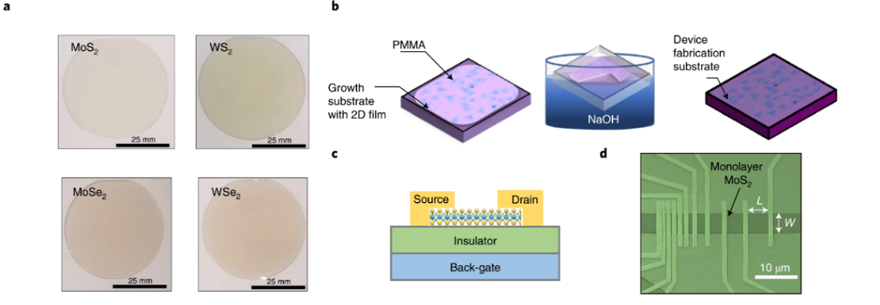

晶圆尺寸二维材料。[1-6]

发展历史

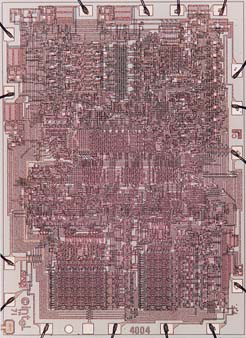

1971年11月,第一款商用微处理器——英特尔4004上市,至今已整整50年。这是一款4位CPU(4 bit),集成了约2300个晶体管,采用10 μm制程,最高主频只有740 kHz,尺寸3 mm × 4 mm,被嵌入到一个16针的封装中。五十年后,第12代英特尔CoreTM i7处理器由上百万晶体管组成,采用了10 nm工艺,最高主频可达5 GHz。五十年间,器件结构、制备方法、电路设计等方面都进行了无数次创新,然而,有一件事保持不变——硅,仍然是微电子产业的基础。

Inter 4004处理器。图片来源:Nat. Electron. [7]

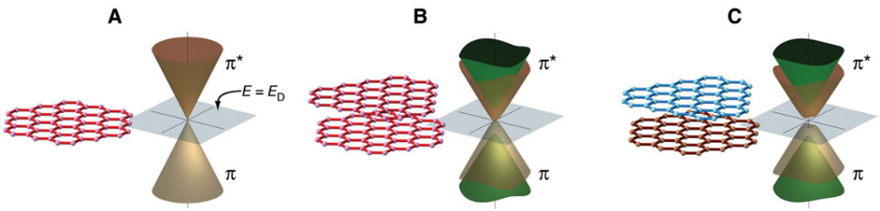

随着硅基器件即将达到摩尔定律极限,10 nm以下的工艺技术越来越具有挑战性。如果将场效应晶体管(FET)沟道宽度降低至亚1纳米范围,将使得沟道-电介质界面处电荷载流子散射急剧增加,并导致三维半导体晶体的迁移率严重降低。石墨烯——于2004年被剥离出来——这种二维材料具有高迁移率,不存在悬空键的单层结构有助于电子-空穴传输,抑制沟道-电介质界面散射。然而,如何将这种零带隙材料改性为半导体,又变成一项艰巨的任务。

石墨烯狄拉克点。图片来源:Science [8]

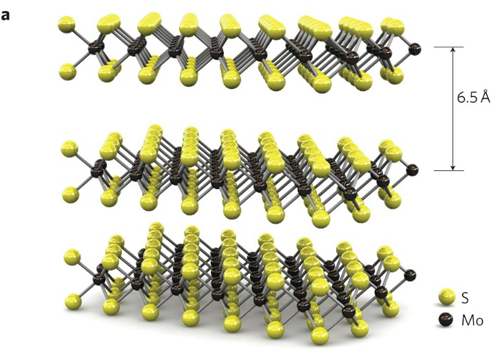

2008年,博士毕业不久的Andras Kis来到瑞士洛桑联邦理工学院工作。他决定带领课题组采取一种不同的方法:如果石墨烯很难变成半导体,那么为什么不直接利用一种本身就具有带隙的二维材料呢 [9]?于是,他们锁定了MoS2作为研究对象,并从辉钼矿中成功剥离出单层MoS2(直接带隙~1.8 eV),基于其制备的晶体管迁移率高达~200 cm2 V−1 s−1,该工作于2011年发表在Nature Nanotechnology 杂志上,论文标题言简意赅“Single-layer MoS2 transistors” [10],几个词就概况了论文的最大亮点,霸气十足!

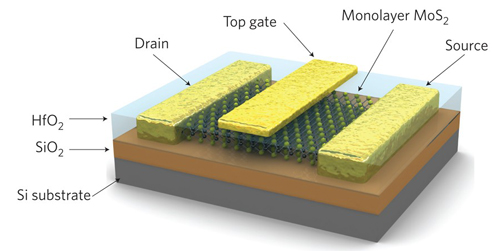

单层MoS2与晶体管器件示意图。图片来源:Nat. Nanotech. [10]

二维生长

尽管机械剥离具有简单、高效、快速试错等诸多优势,但这种策略制备成本及制成品尺寸的限制使其更适合发表论文,在实际工业生产中缺乏可行性。如果使TMDs应用于集成电路的制备,晶圆级合成是不可避免的,化学气相沉积(CVD)和金属-有机化学气相沉积(MOCVD)技术于是脱颖而出。不过,这些生长工艺温度通常大于500 °C,而根据International Roadmap for Devices and Systems(IRDS)建议的标准,CMOS工艺兼容性要求TMDs生长温度低于450 °C。目前报道的CVD方法通常将TMDs外延生长在蓝宝石基底上,这大大减少了晶界数量,同时避免了温度兼容性问题。但是,随之而来的第二个难题是,如何将其清洁且无损地转移,以及之后的光刻、沉积等过程中,如何在不破坏二维材料结构的前提下去除残留物,这些工艺设计往往会影响器件的性能。

基于二维材料的FET。图片来源:Nat. Electron.

晶体管构建

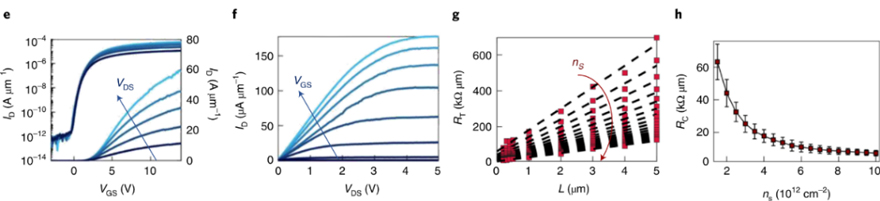

随着二维材料在晶体管中的应用,各种顶栅、底栅、分栅、全环绕栅极结构被制备并研究。开态电流(ION)、关态电流(IOFF)、电流开/关比、载流子迁移率(μ)、阈值电压(VTH)、亚阈值摆幅(SS)、接触电阻(RC)、饱和漂移速度(vSAT)等作为衡量器件性能的关键指标。值得注意的是,对于二维器件,载流子迁移率没有通常假设的那么重要,因为纳米级晶体管中的电流将更多地受到接触电阻、饱和漂移速度或自加热等因素限制。

二维FET的性能表征。图片来源:Nat. Electron.

比如,在二维FET性能测量过程中,饱和区电流经常受到饱和漂移速度和自加热问题的影响。尤其是后者,由于大电流带来发热效应,随着温度升高、散射增加而引起。这将大大降低晶体管的性能和可靠性,饱和区电流密度与阈值电压呈近乎线性的关系,使得器件性能解释变得更加复杂。

饱和漂移速度和自加热现象对二维FET性能影响。图片来源:Nat. Electron.

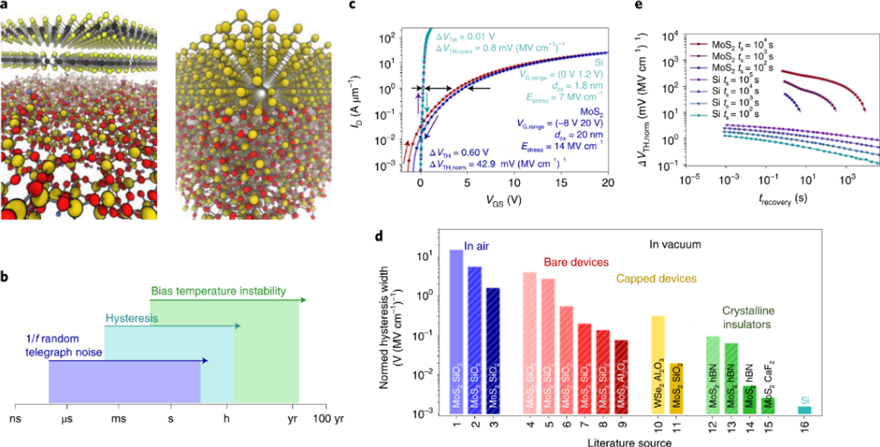

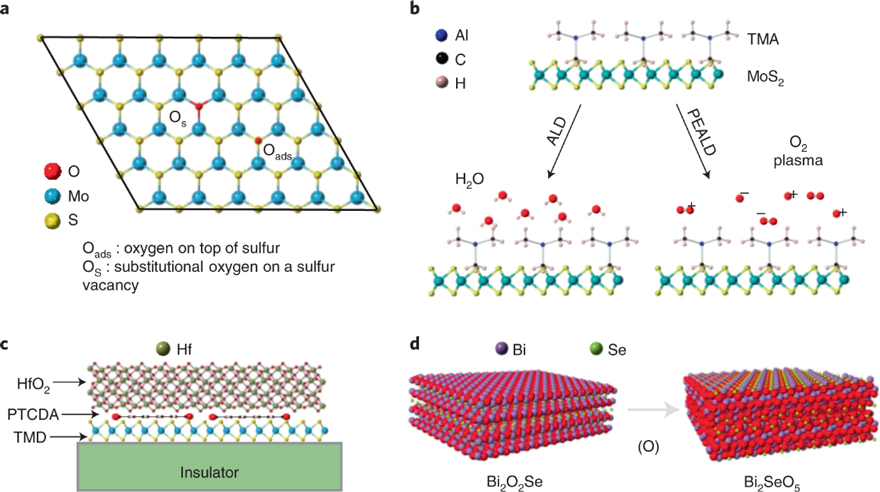

选择合适的绝缘层也是二维FET亟待解决的问题。硅基器件通常使用的SiO2绝缘层,可能导致更多的MoS2/SiO2界面缺陷。随机电报信号(random telegraph signal)用来反映器件的可靠性以及缺陷问题,然而,报道的器件中电荷陷阱的平均时间常数覆盖范围极广,从纳秒一直到年。半导体沟道和绝缘体界面处的缺陷还导致了传输中的滞后现象,这比商业硅基晶体管大了几个数量级,尽管有研究者巧妙地利用滞后效应制备了非易失性存储元件和神经形态电路。采用缺陷较少的晶体做绝缘层,如h-BN、云母、Bi2SeO5、CaF2等有助于减少界面缺陷,或许可以提高二维FET的可靠性,不过这些新型绝缘层还有待进一步研究。到目前为止,制造缺陷密度足够低(< 1012 cm−2)的高质量二维FET仍然是个挑战。

二维FET可靠性研究。图片来源:Nat. Electron.

机遇与挑战

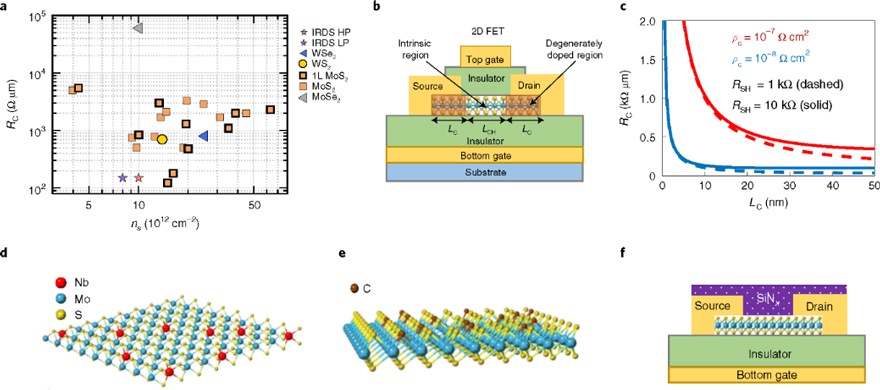

根据IRDS的推测,2028年二维FET将迎来10 nm节点,开态电流100 μA μm−1~1 mA μm−1,高功率和低功率下的关态电流分别为10 nA μm−1 和100 pA μm−1 [11]。研究者认为,接触电阻、掺杂、高κ介电层和器件可靠性是实现高性能二维 FET规模化生产的主要挑战。首先是如何降低接触电阻,迄今为止,报道的MoS2-FET接触电阻最低约为123 Ω μm [12],主要来自于电极-半导体界面的肖特基势垒、金属氧化、金属反应、二维材料缺陷等因素。双栅极器件或许也是未来几代二维FET最适合的结构,可以有效避免源漏电极触点和栅极之间的电容重叠。

其次,二维半导体掺杂正在受到研究者的广泛关注。比如,通过引入半径近似的阳离子(如铌、铼等)或阴离子(如碳、氮等),在不破坏主体材料晶体结构的前提下,实现p型或n型掺杂。掺杂也可以通过绝缘层诱导,例如氧化铝、三氧化钼或氮化硅等材料,抑或是等离子体处理,当然,这些掺杂方法在稳定性、图案化和制造工艺兼容性等方面还存在不小的挑战。

二维FET的接触电阻和掺杂。图片来源:Nat. Electron.

利用CVD法制备的大多数二维材料,载流子迁移率还远低于理论预测值,相比于机械剥离法也有一定差距,这表明晶体缺陷、晶界数量以及晶粒大小等方面还存在很大的改进空间。此外,实现纳米尺寸二维FET的纳米接触、超薄高κ介电层材料的筛选及集成工艺以及保证器件成品率和可靠性等,都是决定二维FET何时才能走向商业化VLSI的限制因素与挑战。

二维FET的高κ介质层的常用集成方法。图片来源:Nat. Electron.

VLSI应用

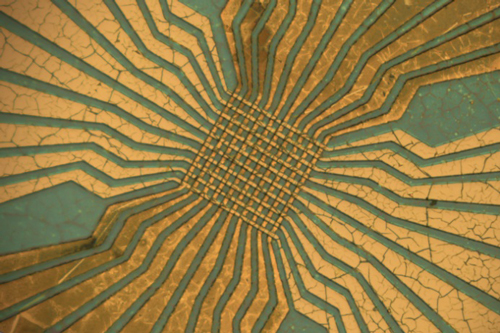

二维FET已经表现出超越硅基FET的巨大潜力,在微/纳电子学器件、三维集成、人工智能、传感等领域有望实现飞跃式发展。对于传统电子学器件,基于二维FET的CMOS逻辑电路、各种非易失性存储器已被广泛研究。这些工艺积累为二维材料在大规模、密集型的三维集成应用提供了可能。此外,利用二维材料单层超薄的特点,在电路互连技术、非冯诺依曼架构的神经形态电路、超灵敏传感器等领域中也能找到潜在的应用。

基于二维材料的10×10忆阻器显微照片。图片来源:Nat. Electron. [13]

正如Saptarshi Das教授所说,“我们相信,在现有的硅基平台上直接生长晶态无缺陷的二维TMDs,以及从生长基板上清洁无损伤的晶圆级转移,是实现进一步VLSI研究的关键”。各大半导体公司,包括台积电(TSMC)在内,正在投入大量的研究资源开发二维材料。二维材料有潜力推动电子行业未来的创新与发展,与工业兼容的合成和制造方法是研究者探索的首要任务。尽管硅材料在未来一段时间内无疑还是半导体行业的核心,作者相信,基于二维材料的商业电子产品的前景并不遥远。

原文(扫描或长按二维码,识别后直达原文页面,或点此查看原文):

Transistors based on two-dimensional materials for future integrated circuits

Saptarshi Das, Amritanand Sebastian, Eric Pop, Connor J. McClellan, Aaron D. Franklin, Tibor Grasser, Theresia Knobloch, Yury Illarionov, Ashish V. Penumatcha, Joerg Appenzeller, Zhihong Chen, Wenjuan Zhu, Inge Asselberghs, Lain-Jong Li, Uygar E. Avci, Navakanta Bhat, Thomas D. Anthopoulos & Rajendra Singh

Nat. Electron., 2021, 4, 786-799, DOI: 10.1038/s41928-021-00670-1

参考文献:

[1] T. Li, et al. Epitaxial growth of wafer-scale molybdenum disulfide semiconductor single crystals on sapphire. Nat. Nanotechnol. 2021, 16, 1201-1207. DOI: 10.1038/s41565-021-00963-8

[2] N. Li, et al. Large-scale flexible and transparent electronics based on monolayer molybdenum disulfide field-effect transistors. Nat. Electron. 2020, 3, 711-717. DOI: 10.1038/s41928-020-00475-8

[3] X. Feng, et al. Self-Selective Multi-Terminal Memtransistor Crossbar Array for In-Memory Computing. ACS Nano 2021, 15, 1764-1774. DOI: 10.1021/acsnano.0c09441

[4] M. Kim, et al. High-Crystalline Monolayer Transition Metal Dichalcogenides Films for Wafer-Scale Electronics. ACS Nano 2021, 15, 3038-3046. DOI: 10.1021/acsnano.0c09430

[5] J. Wang, et al. Dual-coupling-guided epitaxial growth of wafer-scale single-crystal WS2 monolayer on vicinal a-plane sapphire. Nat. Nanotechnol. 2021, DOI: 10.1038/s41565-021-01004-0

[6] List Of Thin Film Samples Available

[7] F. Faggin, How we made the microprocessor. Nat. Electron. 2018, 1, 88. DOI: 10.1038/s41928-017-0014-8

[8] T. Ohta, et al. Controlling the Electronic Structure of Bilayer Graphene. Science, 2006, 313, 951-954. DOI: 10.1126/science.1130681

[9] A. Kis, How we made the 2D transistor. Nat. Electron. 2021, 4, 853. DOI: 10.1038/s41928-021-00675-w

[10] B. Radisavljevic, et al. Single-layer MoS2 transistors. Nature Nanotech 2011, 6, 147-150. DOI: 10.1038/nnano.2010.279

[11] International Roadmap for Devices and Systems (IEEE, 2020);

https://irds-ieee-org.ejproxy.a-star.edu.sg/editions/2020

[12] P.-C. Shen, et al. Ultralow contact resistance between semimetal and monolayer semiconductors. Nature 2021, 593, 211-217. DOI: 10.1038/s41586-021-03472-9

[13] A two-dimensional outlook. Nat. Electron. 2021, 4, 767. DOI: 10.1038/s41928-021-00682-x

(本文由小希供稿)

如果篇首注明了授权来源,任何转载需获得来源方的许可!如果篇首未特别注明出处,本文版权属于 X-MOL ( x-mol.com ), 未经许可,谢绝转载!

-

基于二维材料MoO3的类神经突触晶体管和忆阻器 2017-08-25

-

全集成微型准二维分子晶体薄膜场效应晶体管 2019-08-12

-

二维纳米材料晶体管传感器 2018-02-27

-

二维材料产业化,路还有多远? 2019-09-06

-

缺陷工程调制二维半导体材料 2019-06-03

-

基于二维Janus材料范德华金属-半导体-金属结构中的非对称肖特基接触 2020-11-27

京公网安备 11010802027423号

京公网安备 11010802027423号