当前位置:

X-MOL 学术

›

Adv. Funct. Mater.

›

论文详情

Our official English website, www.x-mol.net, welcomes your

feedback! (Note: you will need to create a separate account there.)

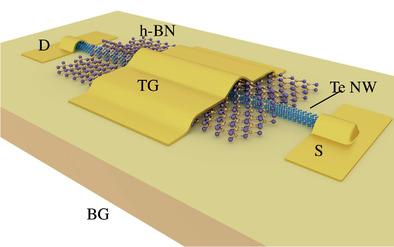

Contact‐Barrier Free, High Mobility, Dual‐Gated Junctionless Transistor Using Tellurium Nanowire

Advanced Functional Materials ( IF 18.5 ) Pub Date : 2021-01-15 , DOI: 10.1002/adfm.202006278 Pushkar Dasika 1 , Debadarshini Samantaray 2 , Krishna Murali 1 , Nithin Abraham 1 , Kenji Watanbe 3 , Takashi Taniguchi 4 , N Ravishankar 2 , Kausik Majumdar 1

Advanced Functional Materials ( IF 18.5 ) Pub Date : 2021-01-15 , DOI: 10.1002/adfm.202006278 Pushkar Dasika 1 , Debadarshini Samantaray 2 , Krishna Murali 1 , Nithin Abraham 1 , Kenji Watanbe 3 , Takashi Taniguchi 4 , N Ravishankar 2 , Kausik Majumdar 1

Affiliation

|

The gate‐all‐around nanowire transistor, due to its extremely tight electrostatic control and vertical integration capability, is a highly promising candidate for sub‐5 nm technology nodes. In particular, the junctionless nanowire transistors are highly scalable with reduced variability due to avoidance of steep source/drain junction formation by ion implantation. Here a dual‐gated junctionless nanowire p‐type field effect transistor is demonstrated using tellurium nanowire as the channel. The dangling‐bond‐free surface due to the unique helical crystal structure of the nanowire, coupled with an integration of dangling‐bond‐free, high quality hBN gate dielectric, allows for a phonon‐limited field effect hole mobility of 570 cm2 V−1 s−1 at 270 K, which is well above state‐of‐the‐art strained Si hole mobility. By lowering the temperature, the mobility increases to 1390 cm2 V−1 s−1 and becomes primarily limited by Coulomb scattering. The combination of an electron affinity of ≈4 eV and a small bandgap of tellurium provides zero Schottky barrier height for hole injection at the metal‐contact interface, which is remarkable for reduction of contact resistance in a highly scaled transistor. Exploiting these properties, coupled with the dual‐gated operation, we achieve a high drive current of 216 μA μm−1 while maintaining an on‐off ratio in excess of 2 × 104. The findings have intriguing prospects for alternate channel material based next‐generation electronics.

中文翻译:

使用碲纳米线的无接触无阻,高迁移率,双栅极无结晶体管

环栅纳米线晶体管由于其极强的静电控制能力和垂直集成能力,是5纳米以下技术节点的极有希望的候选者。特别地,由于避免了通过离子注入形成陡峭的源极/漏极结,因此无结纳米线晶体管是高度可缩放的,并且具有减小的可变性。在此演示了使用碲纳米线作为沟道的双门无结纳米线p型场效应晶体管。由于纳米线具有独特的螺旋晶体结构,因此无悬挂键的表面,加上无悬挂键的高质量hBN栅极电介质的集成,可实现声子受限的场效应空穴迁移率570 cm 2 V -1秒-1在270 K时,这远远高于最新的应变Si空穴迁移率。通过降低温度,迁移率增加至1390cm 2 V -1 s -1,并且主要受到库仑散射的限制。的电子亲和力的组合≈ 4 eV和碲的小带隙提供零用于在金属接触界面的空穴注入,这是显着的用于在高度缩小的晶体管减少接触电阻的肖特基势垒高度。利用这些特性,再加上双门操作,我们可实现216μAμm -1的高驱动电流,同时保持开/关比超过2 × 10 4。。这些发现对于基于替代通道材料的下一代电子产品具有诱人的前景。

更新日期:2021-03-24

中文翻译:

使用碲纳米线的无接触无阻,高迁移率,双栅极无结晶体管

环栅纳米线晶体管由于其极强的静电控制能力和垂直集成能力,是5纳米以下技术节点的极有希望的候选者。特别地,由于避免了通过离子注入形成陡峭的源极/漏极结,因此无结纳米线晶体管是高度可缩放的,并且具有减小的可变性。在此演示了使用碲纳米线作为沟道的双门无结纳米线p型场效应晶体管。由于纳米线具有独特的螺旋晶体结构,因此无悬挂键的表面,加上无悬挂键的高质量hBN栅极电介质的集成,可实现声子受限的场效应空穴迁移率570 cm 2 V -1秒-1在270 K时,这远远高于最新的应变Si空穴迁移率。通过降低温度,迁移率增加至1390cm 2 V -1 s -1,并且主要受到库仑散射的限制。的电子亲和力的组合≈ 4 eV和碲的小带隙提供零用于在金属接触界面的空穴注入,这是显着的用于在高度缩小的晶体管减少接触电阻的肖特基势垒高度。利用这些特性,再加上双门操作,我们可实现216μAμm -1的高驱动电流,同时保持开/关比超过2 × 10 4。。这些发现对于基于替代通道材料的下一代电子产品具有诱人的前景。

京公网安备 11010802027423号

京公网安备 11010802027423号